【導讀】ANSI EIA/TIA-644標準定義的低電壓差分信號(LVDS)非常適合包括時(shí)鐘分配、點(diǎn)對點(diǎn)以及多點(diǎn)之間的信號傳輸。低電壓差分信號(LVDS)非常適合時(shí)鐘分配、一點(diǎn)到多點(diǎn)之間的信號傳輸。本文描述了使用LVDS將高速信號分配到多個(gè)目的端的方法。

在一個(gè)數字系統中,當各個(gè)子系統需要相同的參考時(shí)鐘源協(xié)同工作時(shí),時(shí)鐘分配非常重要。例如,一個(gè)基站的數字信號處理單元(DSP),在大部分應用中,必須由射頻處理單元同步。由鎖相環(huán)(PLL)產(chǎn)生所需的本振頻率,通過(guò)模/數轉換器鎖定到時(shí)鐘中心頻率上。同時(shí),當應用系統中包含射頻接收回路時(shí),時(shí)鐘(包括信號部分)必須盡可能降低傳輸過(guò)程中的電平輻射,使用較低的電平以避免干擾。

將高速信號傳輸到不同目的端時(shí),可以采用多種策略;在這些方案中有兩種極AC端形式:一、用1個(gè)源/驅動(dòng)器驅動(dòng)所有目標端(稱(chēng)為多節點(diǎn)傳輸);二、每個(gè)目標端使用獨立的源/驅動(dòng)器(稱(chēng)為多路點(diǎn)到點(diǎn)傳輸)。圖1展示了利用兩種不同技術(shù)的傳輸方案的區別。在多節點(diǎn)傳輸方式中,需要一個(gè)具有足夠驅動(dòng)能力的驅動(dòng)器來(lái)驅動(dòng)所有負載和傳輸介質(zhì)(電纜、連接器、背板等)。差分總線(xiàn)通常在最后一個(gè)接收器處根據特性阻抗進(jìn)行終端匹配。必須努力使總線(xiàn)上的各支路盡可能短,以避免影響信號的完整性。在電路板布線(xiàn)密度日益提高的今天,有些情況下很難控制分支長(cháng)度。

圖1. 多節點(diǎn)信號傳輸允許在單個(gè)發(fā)送器與多個(gè)接收器之間通訊,而多路點(diǎn)到點(diǎn)傳輸方式無(wú)需調整分支回路,消除了分支回路的潛在干擾問(wèn)題。

相應地,多路點(diǎn)到點(diǎn)傳輸方式使用了多個(gè)驅動(dòng)器,只需明確點(diǎn)到點(diǎn)操作模式,每個(gè)驅動(dòng)器只與單個(gè)接收器通信。采用這種設計架構可以避免信號完整性問(wèn)題,確保傳輸介質(zhì)的阻抗盡可能一致。

下面將要介紹的一款低抖動(dòng)10端口LVDS轉接器MAX9150可以用于多路點(diǎn)到點(diǎn)信號傳輸。

MAX9150 LVDS轉接器

MAX9150適用于對電源功耗、電路板空間以及噪聲要求苛刻的高速數據或時(shí)鐘傳輸應用。圖2中的IC能夠接收1路LVDS信號,并將其驅動(dòng)至10路LVDS輸出。

圖2. MAX9150 LVDS轉接器可以將接收到的輸入信號驅動(dòng)至10路輸出,MAX9110則將其輸入端的CMOS信號轉換成差分信號,MAX9111將各自的LVDS差分信號轉換成CMOS電平信號。

MAX9150的輸入端可以接受幅值最小100mV、最大1V的差分信號,要求輸入信號電平在0至2.4V范圍內。輸出端采用電流激勵產(chǎn)生5至9mA電流輸出。由于MAX9150輸出電流信號,輸出信號的差分電平范圍由外部終端電阻的阻值決定,每個(gè)差分輸出端設計為驅動(dòng)50Ω負載,允許在兩端采用100Ω匹配的傳輸線(xiàn)上以點(diǎn)到點(diǎn)方式傳輸信號。器件具有120ps抖動(dòng)(隨機性和確定性),應用于對時(shí)序誤差敏感的高速互聯(lián)系統可保證通信的可靠性,尤其是編碼信號中嵌入的時(shí)鐘信息。高速開(kāi)關(guān)確保400Mbps的數據傳輸速率和小于100ps的通道間偏差。MAX9150工作電源為3.3V,當傳輸信號為400Mbps時(shí)最大電流消耗為160mA。通過(guò)低功耗關(guān)斷模式,可以將電源電流降低到60µA。當沒(méi)有輸入驅動(dòng)或出現開(kāi)路、終端電阻失效或短路時(shí),器件內的失效保護電路可以將輸出端置為高電平。

表1強調了MAX9150的關(guān)鍵參數。

表1. MAX9150的抖動(dòng)指標

Maxim的其它LVDS器件

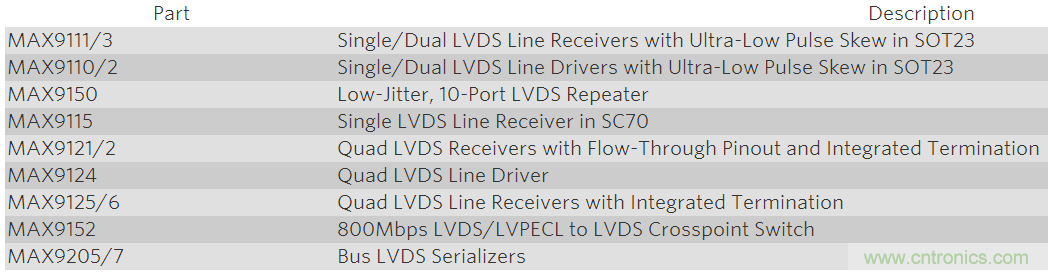

表2列出了Maxim公司的一些LVDS器件,這些器件可以與MAX9150配合使用,也可以單獨使用。圖2給出了其中兩種器件與MAX9150配合使用的例子。在這個(gè)應用中,MAX9110將CMOS電平轉換為L(cháng)VDS信號提供給MAX9150,在傳輸線(xiàn)終端,采用SOT23封裝的MAX9111接收器將LVDS信號重新轉換到CMOS電平。

表2. Maxim提供數量眾多的LVDS IC,包括接收器、驅動(dòng)器、轉接器、交叉開(kāi)關(guān)、總線(xiàn)串行器等

結論

當信號傳輸速率達到數十到數百MHz時(shí),相對于TTL信號傳輸方式,LVDS器件通常是一個(gè)更好的選擇。其差分特性從根本上增強了抗共模干擾能力,而且降低了噪聲。與其它傳輸方式(如ECL、CML等)相比,低功耗也是該傳輸方式的一個(gè)特色,當然,電路的總體功耗通常取決于所選擇的端接技術(shù)?;贚VDS技術(shù)的集成電路適用于很多應用,包括時(shí)鐘分配、高達400MHz以上的串行數據信號傳輸等。上述Maxim的LVDS器件在傳輸這些信號時(shí),僅產(chǎn)生很低的相位抖動(dòng)和少量的功耗,具有極低的干擾。這里展示了兩種信號傳輸方式:多節點(diǎn)傳輸和多路點(diǎn)到點(diǎn)傳輸方式。每種傳輸方式都有自身的優(yōu)點(diǎn)和缺點(diǎn)。

MAX9150芯片構成了高速數據或時(shí)鐘分配系統的核心,其它LVDS器件(如單路/多路驅動(dòng)器等)用于完成電路的特定功能。Maxim也同樣提供LVDS交叉開(kāi)關(guān)、總線(xiàn)串行器等。

本文來(lái)源于Maxim。

推薦閱讀: