【導讀】電源電壓的要求一般在±5%以?xún)?。電流需要根據使用的不同芯片,及芯片個(gè)數等進(jìn)行計算。由于DDR的電流一般都比較大,所以PCB設計時(shí),如果有一個(gè)完整的電源平面鋪到管腳上,是最理想的狀態(tài),并且在電源入口加大電容儲能,每個(gè)管腳上加一個(gè)100nF~10nF的小電容濾波。

1、DDR系統的三種電源

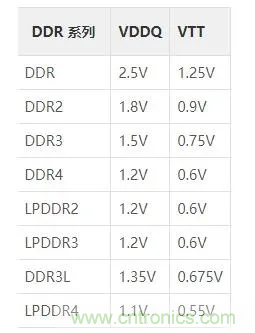

對于電源電壓,DDR SDRAM系統要求三個(gè)電源,分別為VDDQ、VTT和VREF。

A、主電源VDD和VDDQ

主電源的要求是VDDQ=VDD,VDDQ是給IO buffer供電的電源,VDD是給內核供電。但是一般的使用中都是把VDDQ和VDD合成一個(gè)電源使用。

有的芯片還有專(zhuān)門(mén)的VDDL,是給DLL供電的,也和VDD使用同一電源即可。

電源設計時(shí),需要考慮電壓、電流是否滿(mǎn)足要求。

電源的上電順序和電源的上電時(shí)間,單調性等。

電源電壓的要求一般在±5%以?xún)?。電流需要根據使用的不同芯片,及芯片個(gè)數等進(jìn)行計算。由于DDR的電流一般都比較大,所以PCB設計時(shí),如果有一個(gè)完整的電源平面鋪到管腳上,是最理想的狀態(tài),并且在電源入口加大電容儲能,每個(gè)管腳上加一個(gè)100nF~10nF的小電容濾波。

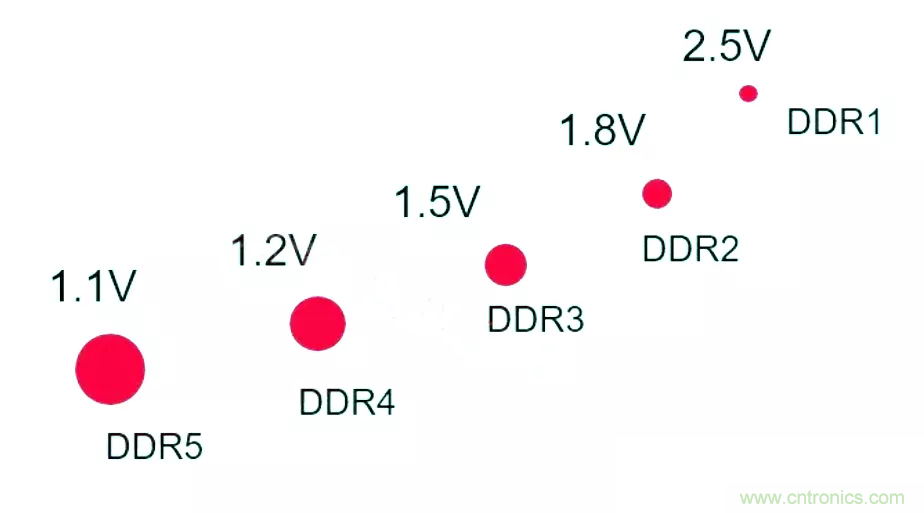

到了DDR5,電壓從1.2V將會(huì )變到1.1V,下降了8.3%,這是幾代DDR總線(xiàn)以來(lái)下降比例最少的一次。說(shuō)明電子技術(shù)的發(fā)展,對于低功耗的設計難度越來(lái)越大。這么低的電壓,其抗干擾設計就會(huì )更加的難。對于電源完整性和信號完整性的設計要求就越來(lái)越嚴苛。

B、參考電源Vref

參考電源Vref要求跟隨VDDQ,并且Vref=VDDQ/2,所以可以使用電源芯片提供,也可以采用電阻分壓的方式得到。由于Vref一般電流較小,在幾個(gè)mA~幾十mA的數量級,所以用電阻分壓的方式,即節約成本,又能在布局上比較靈活,放置的離Vref管腳比較近,緊密的跟隨VDDQ電壓,所以建議使用此種方式。需要注意分壓用的電阻在100Ω~10kΩ均可,需要使用1%精度的電阻。Vref參考電壓的每個(gè)管腳上需要加10nF的電容濾波,并且每個(gè)分壓電阻上也并聯(lián)一個(gè)電容較好。

Vref此處的電流并不大,通過(guò)分壓,可以選擇阻值稍大的電阻。所以需要靠近芯片放置,放置走線(xiàn)過(guò)長(cháng),被其他大電流信號干擾。

C、用于匹配的電壓VTT(Tracking Termination Voltage)

VDDQ是一種高電流電源DDR芯片的內核、I/O和存儲器邏輯供電,而Vref是一種低電流、精確的參考電壓,它在邏輯高電平(1)和邏輯低電平(0)之間提供一個(gè)閾值,以適應I/O電源電壓的變化。通過(guò)提供一個(gè)適應電源電壓的精確閾值,VREF實(shí)現了比固定閾值和終端和驅動(dòng)正常變化情況下更大的噪聲裕度。

VTT是改善信號質(zhì)量,最常見(jiàn)的規格是0.49到0.51倍VDDQ,VTT為匹配電阻上拉到的電源,VTT=VDDQ/2。

DDR的設計中,根據拓撲結構的不同,有的設計使用不到VTT,如控制器帶的DDR器件比較少的情況下。如果使用VTT,則VTT的電流要求是比較大的,所以需要走線(xiàn)使用銅皮鋪過(guò)去。并且VTT要求電源即可以吸電流,又可以灌電流才可以。一般情況下可以使用專(zhuān)門(mén)為DDR設計的產(chǎn)生VTT的電源芯片來(lái)滿(mǎn)足要求。很多情況下,也采用上下拉電阻實(shí)現吸電流和灌電流的功能,即戴維南電路。

而且,每個(gè)拉到VTT的電阻旁一般放一個(gè)10nF~100nF的電容,整個(gè)VTT電路上需要有uF級大電容進(jìn)行儲能。

由于VTT電源必須在 1/2 VDDQ提供和吸收電流,因此如果沒(méi)有通過(guò)分流來(lái)允許電源吸收電流,那么就不能使用一個(gè)標準的開(kāi)關(guān)電源。而且,由于連接到VTT的每條數據線(xiàn)都有較低的阻抗,因而電源就必須非常穩定。在這個(gè)電源中的任何噪聲都會(huì )直接進(jìn)入數據線(xiàn)。

VTT 被用來(lái)從DDR控制器IC中獲取電壓,給數據總線(xiàn)和地址總線(xiàn)提供電源,VTT不直接應用在DDR器件上,而是在系統電源上(VTT和終端電阻都被集成到 DDR CONTROLLER上),因此不需要在電路圖中額外標出。它的值通常設定大致等于VREF的值(在VREF上下0.04V浮動(dòng)),并且隨著(zhù)VREF的變 化而變化。對于DDR1 SDRAM應用中的地址總線(xiàn)控制信號和數據總線(xiàn)信號都有端接電阻。需要一個(gè)沒(méi)有任何的噪聲或者電壓變化的參考電壓(VREF),用作DDR SDRAM輸入接收器,VREF也等于1/2 VDDQ。VREF的變化將會(huì )影響存儲器的設置和保持時(shí)間。

2、為什么需要VTT

為了符合DDR的要求并保證最優(yōu)的性能,VTT和VREF需要在電壓、溫度和噪聲容限上進(jìn)行嚴密的控制以便跟蹤1/2 VDDQ。

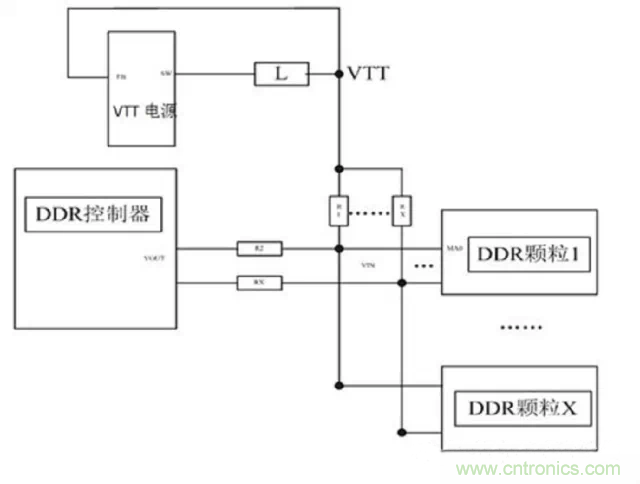

在實(shí)際電路中,對于VREF的電壓采取電阻分壓的方式取得,如下圖所示:

其中電容為去耦電容。

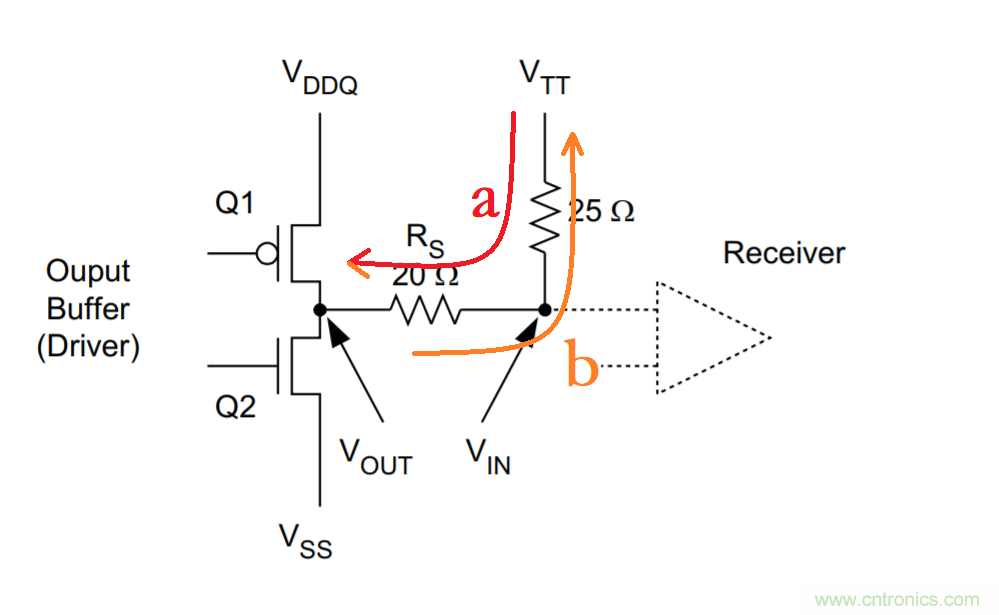

DDR顆粒的接收端比較特殊,它是一個(gè)差分放大器,其中的一個(gè)PIN腳連接Vref是固定,另一個(gè)PIN接在DDR控制器的發(fā)送端,發(fā)送端發(fā)送過(guò)來(lái)的信號,只要比Vref高,高過(guò)一定的門(mén)限,接受端就認為1,只要比Vref低,低于一定的門(mén)限,接收端就認為0。我們知道DDR的速率(電平的切換)是很快的,同時(shí)一個(gè)控制器會(huì )下掛很多顆粒,這就導致總線(xiàn)上的電流(電荷)來(lái)不及泄放和補充,這就需要將VTT在VOUT為高的時(shí)候,吸收電流,在VOUT為低的時(shí)候補充電流;

以DDR2為例,當VOUT為高電平的時(shí)候,VOUT=1V8,VTT=0V9,電流b向處于增加的趨勢,當VOUT為0,VTT=0V9,電流a向處于增加趨勢;

一般DDR VTT的拓撲結構

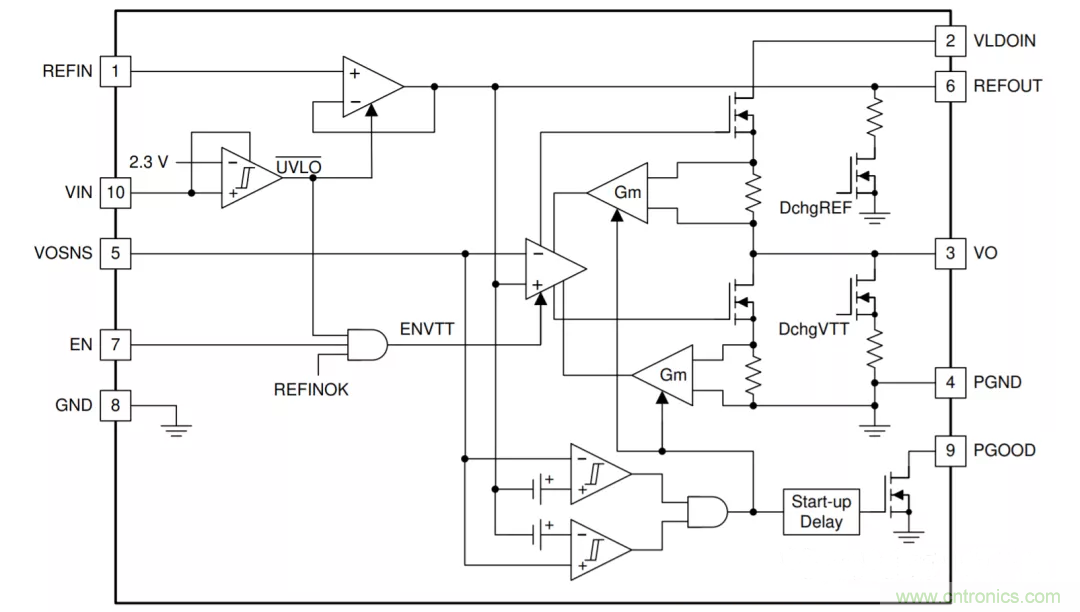

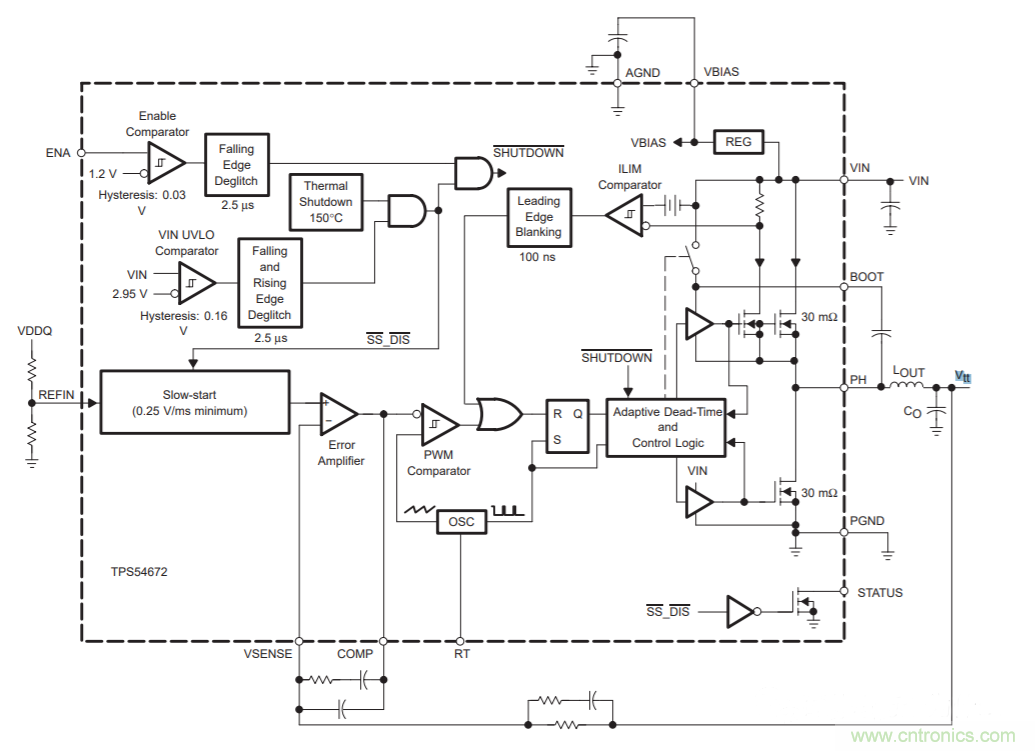

3、VTT電源工作原理

其中VFB為電壓反饋端,SW為電壓輸出端;

結合DDR拓撲圖來(lái)看,當VOUT為低的時(shí)候,由于a方向的電流處于增大的趨勢,電感L會(huì )產(chǎn)生臨時(shí)反向電動(dòng)勢,來(lái)抑制電流變化,這樣導致VTT電壓變小,上管導通,來(lái)補償這個(gè)電流,直至流經(jīng)電感的電流等于新的電流;

當VOUT為高的時(shí)候,由于b方向的電流處于增大的趨勢,電感L會(huì )產(chǎn)生臨時(shí)的反向電動(dòng)勢,來(lái)抑制電流變化,這樣導致VTT處的電源變大,進(jìn)而導致Vsense變大,上管關(guān)閉,下管導通,吸收電流;

4、戴維南電路代替VTT

在一些設計中,在使用DDR顆粒的情況下,已經(jīng)基本全部不使用VTT電源,全部采用電阻上下拉的戴維南電路(用上下拉電阻替代VTT電源),只有在使用內存條的情況下才使用VTT電源。需要進(jìn)行信號完整性仿真之后,確定上下拉電阻的阻值。這個(gè)阻值一般比較小,雖然降低了設計復雜度,但是增大了整個(gè)系統的功耗。

一般情況下,DDR的數據線(xiàn)都是一驅一的拓撲結構,且DDR2和DDR3內部都有ODT做匹配,所以不需要拉到VTT做匹配即可得到較好的信號質(zhì)量。DDR2的地址和控制信號線(xiàn)如果是多負載的情況下,會(huì )有一驅多,并且內部沒(méi)有ODT,其拓撲結構為走T型的結構,所以常常需要使用VTT進(jìn)行信號質(zhì)量的匹配控制。DDR3可以采用Fly-by方式走線(xiàn)。

4、VTT電流預估

例如:VTT(0.6V)作為地址線(xiàn)/控制線(xiàn)(共25根)的上拉電源 ,上拉電阻39.2歐姆,最大電流計算公式:(0.6V/39.2)*25 = 0.38A。

最大電流就是所有信號同為高,或者同為低的時(shí)候,所有的信號線(xiàn)都是灌電流或者拉電流。如果有高有底,則會(huì )相互抵消,VTT的輸出電流沒(méi)有那么大。

(來(lái)源:硬件十萬(wàn)個(gè)為什么)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請電話(huà)或者郵箱聯(lián)系小編進(jìn)行侵刪。