【導讀】在高頻領(lǐng)域,信號或電磁波必須沿著(zhù)具有均勻特征阻抗的傳輸路徑傳播。一旦阻抗失配或不連續現象,一部分信號被反射回發(fā)送端,剩余部分電磁波將繼續被傳輸到接收端。

在高頻領(lǐng)域,信號或電磁波必須沿著(zhù)具有均勻特征阻抗的傳輸路徑傳播。一旦阻抗失配或不連續現象,一部分信號被反射回發(fā)送端,剩余部分電磁波將繼續被傳輸到接收端。

信號反射和衰減的程度取決于阻抗不連續的程度。當失配阻抗幅度增加時(shí),更大部分的信號會(huì )被反射,接收端觀(guān)察到的信號衰減或劣化也就更多。

阻抗失配現象在交流耦合(又稱(chēng)隔直)電容的SMT焊盤(pán)、板到板連接器以及電纜到板連接器(如SMA)處經(jīng)常會(huì )遇到。

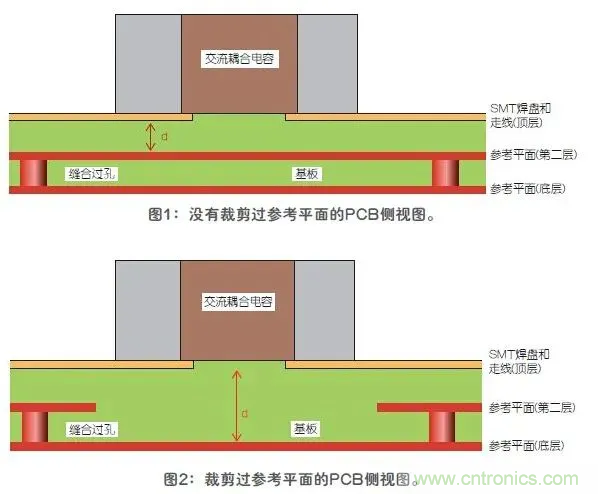

在如圖1所示的交流耦合電容SMT焊盤(pán)的案例中,沿著(zhù)具有100Ω差分阻抗和5mil銅箔寬度的PCB走線(xiàn)傳播的信號,在到達具有更寬銅箔(如0603封裝的30mil寬)的SMT焊盤(pán)時(shí)將遇到阻抗不連續性。這種現象可以用式(1)和式(2)解釋。

銅箔的橫截面積或寬度的增加將增大條狀電容,進(jìn)而給傳輸通道的特征阻抗帶來(lái)電容不連續性,即負的浪涌。

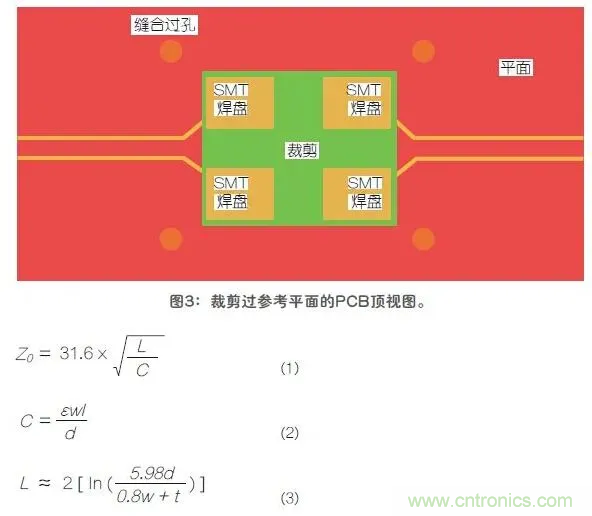

為了盡量減小電容的不連續性,需要裁剪掉位于SMT焊盤(pán)正下方的參考平面區域,并在內層創(chuàng )建銅填充,分別如圖2和圖3所示。

這樣可以增加SMT焊盤(pán)與其參考平面或返回路徑之間的距離,從而減小電容的不連續性。同時(shí)應插入微型縫合過(guò)孔,用于在原始參考平面和內層新參考銅箔之間提供電氣和物理連接,以建立正確的信號返回路徑,避免EMI輻射問(wèn)題。

但是,距離“d ”不應增加得太大,否則將使條狀電感超過(guò)條狀電容并引起電感不連續性。式中:

條狀電容(單位:pF);

條狀電感(單位:nH);

特征阻抗(單位:Ω);

ε=介電常數;

焊盤(pán)寬度;

焊盤(pán)長(cháng)度;焊盤(pán)和下方參考平面之間的距離;

焊盤(pán)的厚度。

相同概念也可以應用于板到板(B2B)和電纜到板(C2B)連接器的SMT焊盤(pán)。

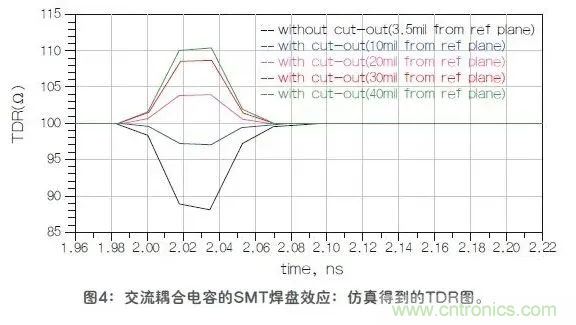

下面將通過(guò)TDR和插損分析完成上述概念的驗證。分析是通過(guò)在EMPro軟件中建立SMT 焊盤(pán)3D 模型, 然后導入Keysight ADS中進(jìn)行TDR和插損仿真完成的。

1、分析交流耦合電容的SMT焊盤(pán)效應

在EMPro中建立一個(gè)具有中等損耗基板的SMT的3D模型,其中一對微帶差分走線(xiàn)長(cháng)2英寸、寬5mil,采用單端模式,與其參考平面距離3.5mil,這對走線(xiàn)從30mil寬SMT焊盤(pán)的一端進(jìn)入,并從另一端引出。

圖4和圖5分別顯示了仿真得到的TDR和插損圖。

參考平面沒(méi)有裁剪的SMT設計造成的阻抗失配是12Ω,插損在20GHz時(shí)為-6.5dB。一旦對SMT焊盤(pán)下方的參考平面區域進(jìn)行了裁剪(其中“d ”設為10mil),失配阻抗就可以減小到2Ω,20GHz時(shí)的插損減小到-3dB。

進(jìn)一步增加“d ”會(huì )導致條狀電感超過(guò)電容,從而引起電感不連續性,轉而使插損變差(即-4.5dB)。

2、分析B2B連接器的SMT焊盤(pán)效應

在EMPro中建立一個(gè)B2B連接器的SMT焊盤(pán)的3D模型,其中連接器引腳間距是20mil,引腳寬度是6mil,焊盤(pán)連接到一對長(cháng)5英寸、寬5mil,采用單端模式的微帶差分走線(xiàn),走線(xiàn)距其參考平面3.5mil。

SMT焊盤(pán)的厚度是40mil,包括連接器引腳和焊錫在內的這個(gè)厚度幾乎是微帶PCB走線(xiàn)厚度的40倍。

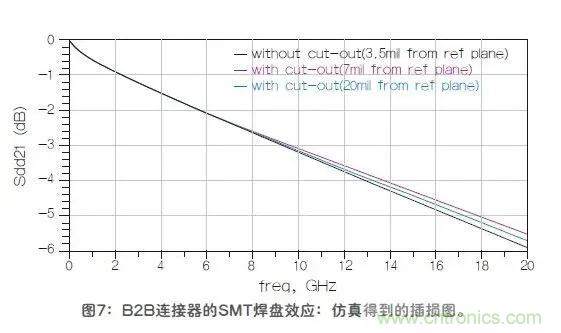

銅厚度的增加將導致電容的不連續性和更高的信號衰減。這種現象可以分別由圖6和圖7所示的TDR和插損仿真圖中看出來(lái)。

通過(guò)裁剪掉SMT焊盤(pán)正下方適當間距“d ”(即7mil)的銅區域,可以最大限度地減小阻抗失配。

3、小結

本文的分析證明,裁剪掉SMT焊盤(pán)正下方的參考平面區域可以減小阻抗失配,增加傳輸線(xiàn)的帶寬。

SMT焊盤(pán)與內部參考銅箔之間的距離取決于SMT焊盤(pán)的寬度,以及包括連接器引腳和焊錫在內的SMT焊盤(pán)有效厚度。在條件允許的情況下,PCB投產(chǎn)之前應先進(jìn)行3D建模和仿真,確保構建的傳輸通道具有良好的信號完整性。

來(lái)源:微波射頻網(wǎng)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請電話(huà)或者郵箱聯(lián)系小編進(jìn)行侵刪。