【導讀】從20nm技術(shù)節點(diǎn)開(kāi)始,漏電流一直都是動(dòng)態(tài)隨機存取存儲器(DRAM)設計中引起器件故障的主要原因。即使底層器件未出現明顯的結構異常,DRAM設計中漏電流造成的問(wèn)題也會(huì )導致可靠性下降。漏電流已成為DRAM器件設計中至關(guān)重要的一個(gè)考慮因素。

從20nm技術(shù)節點(diǎn)開(kāi)始,漏電流一直都是動(dòng)態(tài)隨機存取存儲器(DRAM)設計中引起器件故障的主要原因。即使底層器件未出現明顯的結構異常,DRAM設計中漏電流造成的問(wèn)題也會(huì )導致可靠性下降。漏電流已成為DRAM器件設計中至關(guān)重要的一個(gè)考慮因素。

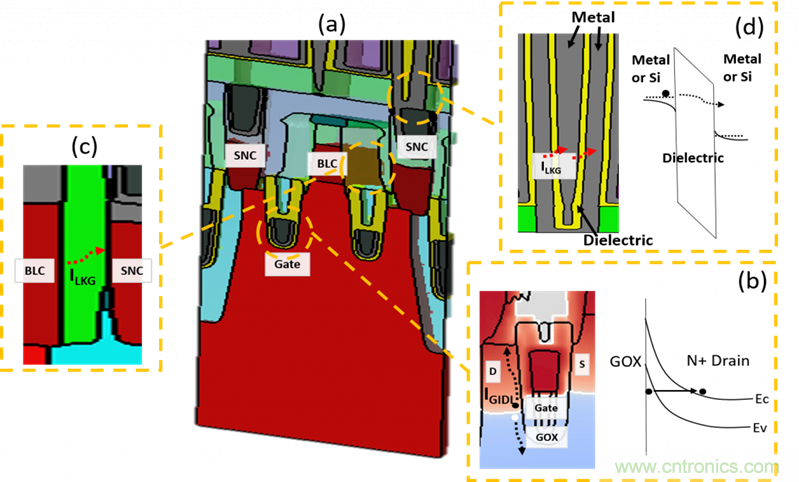

圖1. (a) DRAM存儲單元;(b)單元晶體管中的柵誘導漏極泄漏電流 (GIDL);(c)位線(xiàn)接觸 (BLC) 與存儲節點(diǎn)接觸 (SNC) 之間的電介質(zhì)泄漏;(d) DRAM電容處的電介質(zhì)泄漏。

DRAM存儲單元(圖1 (a))在電源關(guān)閉時(shí)會(huì )丟失已存儲的數據,因此必須不斷刷新。存儲單元在數據丟失前可存儲數據的時(shí)間, 即保留時(shí)間,是DRAM的一個(gè)關(guān)鍵特性,保留時(shí)間的長(cháng)短會(huì )受到漏電流的限制。

有兩種重要的漏電機制會(huì )影響DRAM的數據保留時(shí)間。第一種是單元晶體管漏電。DRAM中的單元晶體管漏電主要由于柵誘導漏極泄漏電流(GIDL)(圖1 (b)),它是由漏結處高電場(chǎng)效應引起的漏電流。在負柵偏置下,柵極會(huì )產(chǎn)生一個(gè)耗盡區(N+漏極區),該耗盡區進(jìn)而在區域中產(chǎn)生一個(gè)增強電場(chǎng),這個(gè)電場(chǎng)造成的能帶彎曲則導致了帶間隧穿(BTBT)。此時(shí),在柵極移動(dòng)的電子和少數載流子可以穿過(guò)隧道進(jìn)入漏極,從而產(chǎn)生不必要的漏電流。

DRAM中的第二種漏電機制是位線(xiàn)接觸 (BLC) 與存儲節點(diǎn)接觸 (SNC) 之間的電介質(zhì)泄漏(圖1 (c))。電介質(zhì)泄漏通常發(fā)生在電容內部,此時(shí)電子流過(guò)金屬和介電區域(圖1 (d))。當電子通過(guò)電介質(zhì)層從一個(gè)電極隧穿到另一個(gè)電極時(shí),便會(huì )引起電介質(zhì)泄漏。隨著(zhù)工藝節點(diǎn)的縮小,BLC和SNC之間的距離也在逐漸縮短,因此,這個(gè)問(wèn)題正在變得愈發(fā)嚴重。這些結構元件的制造工藝偏差也會(huì )對位線(xiàn)接觸和存儲節點(diǎn)接觸之間的電介質(zhì)泄漏產(chǎn)生負面影響。

虛擬制造平臺SEMulator3D®可使用設計和工藝流數據來(lái)構建DRAM器件的3D模型。完成器件的“虛擬”制造之后,用戶(hù)可通過(guò)SEMulator3D查看器從任意方向觀(guān)察漏電路徑,并且可以計算推導出總的漏電值。這一功能對了解工藝變化對DRAM漏電流的影響大有幫助。SEMulator3D中的漂移/擴散求解器能提供電流-電壓 (IV) 分析,包括GIDL和結點(diǎn)漏電計算,以實(shí)現一體化設計技術(shù)的協(xié)同優(yōu)化。用戶(hù)還可以通過(guò)改變設計結構、摻雜濃度和偏置強度,來(lái)查看漏電值的變化。

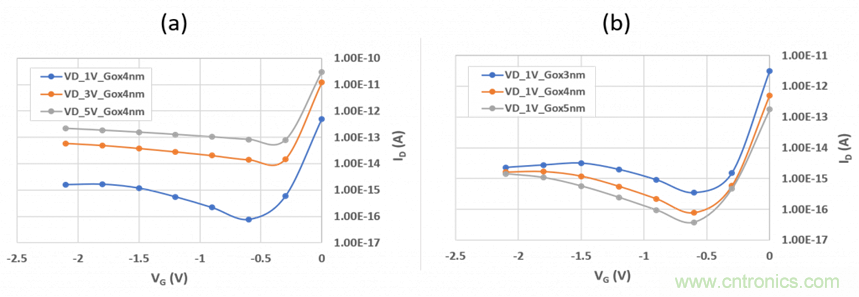

圖2. (a)在不同漏極電壓下,柵極電壓和漏極電流的變化曲線(xiàn);(b)在不同柵極氧化層厚度 (+/-1nm) 下,柵極電壓和漏極電流的變化曲線(xiàn)。

圖2表明GIDL會(huì )隨著(zhù)柵極氧化層厚度的變化而增加。柵極氧化層越薄,建模器件的柵極與漏極之間的電勢越高。

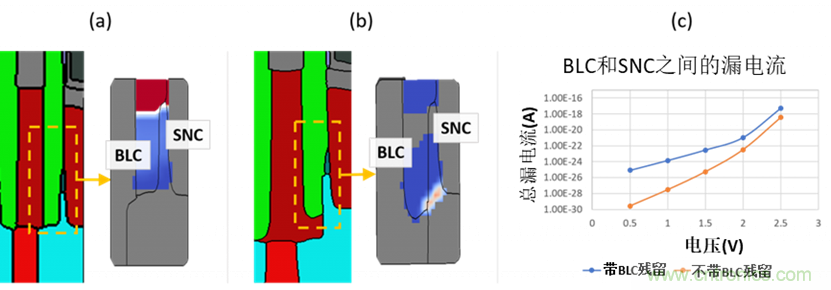

圖3. (a)和(b)帶BLC殘留和不帶BLC殘留結構中BLC和SNC之間的漏電流;(c)電壓掃描下總漏電流的變化。

圖3顯示了SEMulator3D中的電介質(zhì)泄漏路徑以及位線(xiàn)接觸和存儲節點(diǎn)接觸之間的總電流差,突出了刻蝕工藝過(guò)程中BLC的制造偏差帶來(lái)的影響。如圖3 (c)所示,由于工藝偏差的影響,帶BLC殘留結構的總漏電流高于不帶BLC殘留結構的總漏電流。

圖4. (a) DRAM電容Z平面截面圖像及電介質(zhì)泄漏路徑;(b)電容X平面界面圖像及電介質(zhì)泄漏路徑;(c)總漏電流與偏置強度的變化曲線(xiàn)。

圖4所示為DRAM電容的電介質(zhì)泄漏的例子。圖4 (a)和4 (b)分別是DRAM的Z平面和X平面截面圖,以及在SEMulator3D器件模型中觀(guān)察到的電介質(zhì)泄漏路徑在這兩個(gè)平面上的投影。圖4 (c)顯示了位于底層 (BTM) 電極的漏電流隨著(zhù)外加的偏置而變化。

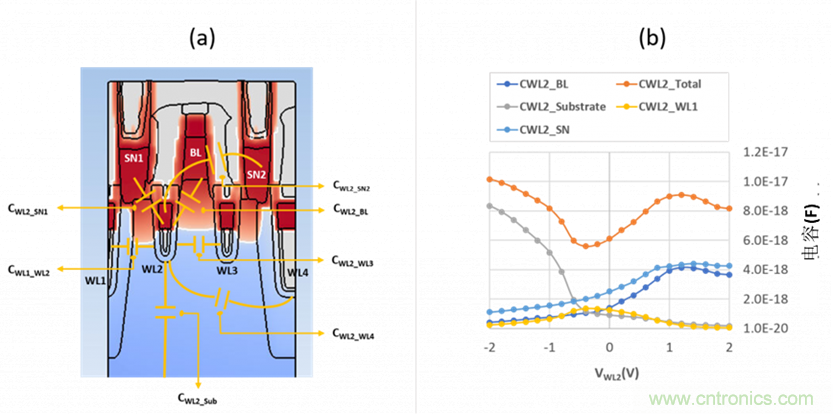

圖5. (a) DRAM單元的摻雜濃度視圖,顯示了將交流信號施加到字線(xiàn)WL2時(shí),字線(xiàn)WL2和其他節點(diǎn)處的電容類(lèi)型(和預期位置);(b)字線(xiàn)WL2和器件上其他節點(diǎn)之間的電容計算值。

影響DRAM性能的另一個(gè)重要因素是器件的寄生電容。DRAM開(kāi)發(fā)期間應進(jìn)行交流(AC)分析,因為位線(xiàn)耦合會(huì )導致寫(xiě)恢復時(shí)間(tWR)延遲,并產(chǎn)生其他性能故障。由于摻雜的多晶硅不僅用于晶體管柵極,還用于位線(xiàn)接觸和存儲節點(diǎn)接觸,這會(huì )導致多個(gè)潛在的寄生電容產(chǎn)生(見(jiàn)圖5 (a)),所以必須對整個(gè)器件進(jìn)行電容測量。SEMulator3D內置AC分析功能,可測量復雜的模擬3D結構的寄生電容值。例如,通過(guò)模擬將交流小信號施加到字線(xiàn)WL2,SEMulator3D可以獲取全新設計的DRAM結構中字線(xiàn)WL2與其它所有節點(diǎn)之間的電容值,以及它們隨著(zhù)電壓變化而變化的曲線(xiàn)(圖5 (b))。

總而言之,多種來(lái)源的漏電流和寄生電容會(huì )引起DRAM的故障。在DRAM開(kāi)發(fā)期間,工程師需仔細評估這些故障模式,當然也應該考慮工藝變化對漏電流和寄生電容的影響。通過(guò)使用預期工藝流程和工藝變化來(lái)“虛擬”構建3D器件,然后分析不同工藝條件下的寄生和晶體管效應,可以簡(jiǎn)化DRAM的下一代尋徑過(guò)程。SEMulator3D集成了3D工藝模型、R/C分析和器件分析功能,可以快速地驗證DRAM器件結構在不同工藝假設下是否容易發(fā)生漏電流或寄生電容故障。

Reference

1. M. T. Bohr, “Nanotechnology Goals and Challenges for Electronic Applications,” IEEE Trans. on Nanotechnology, 1, 1, 56-62 (2002)

2. J. H. Chen, S. C. Wong, Y. H. Wang, “An analytical three terminal Band-to-Band tunneling model on GIDL in MOSFET,” IEEE Trans. on Electron devices, 48, 1400-1405 (2001)

(來(lái)源:電子創(chuàng )新網(wǎng),作者:Tae Yeon Oh, 泛林集團半導體工藝及整合高級工程師)

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請聯(lián)系小編進(jìn)行處理。