【導讀】電路設計過(guò)程中,應用工程師往往會(huì )忽視印刷電路板(PCB)的布局。通常遇到的問(wèn)題是,電路的原理圖是正確的,但并不起作用,或僅以低性能運行。

那如何正確地布設運算放大器的電路板以確保其功能、性能和穩健性呢?

事件重現

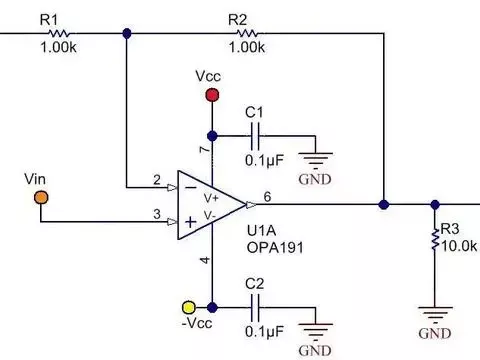

工程師與自己的實(shí)習生利用增益為2V/V、負荷為10k、電源電壓為+/-15V的非反相配置OPA191運算放大器進(jìn)行設計。圖1所示為該設計的原理圖。

圖1 采用非反相配置的OPA191原理圖

工程師指派實(shí)習生為該設計布設電路板,同時(shí)為他做了PCB布設方面的一般指導(即盡可能縮短電路板的走線(xiàn)路徑,同時(shí)將組件保持緊密排布,以減小電路板空間),然后讓他自行設計。

設計過(guò)程到底有多難?其實(shí)就是幾個(gè)電阻器和電容器罷了,不是嗎?

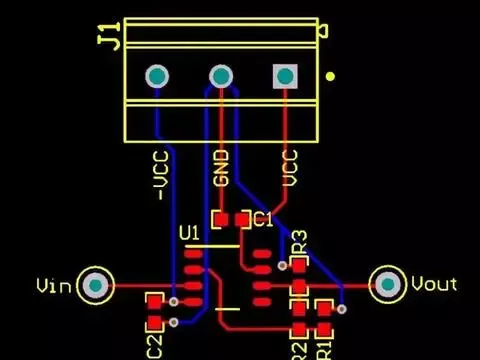

圖2所示為實(shí)習生首次嘗試設計的布局。紅線(xiàn)為電路板頂層的路徑,而藍線(xiàn)為底層的路徑。

圖2 首次布局嘗試方案

當時(shí)意識到電路板布局并不像自己想象的那樣直觀(guān),工程師覺(jué)得應該為實(shí)習生做一些更詳細的指導。實(shí)習生在設計時(shí)完全遵從了他的建議,縮短了走線(xiàn)路徑,并將各部件緊密地排布在一起。但這種布局還可以進(jìn)一步改善,從而減小電路板寄生阻抗并優(yōu)化其性能。

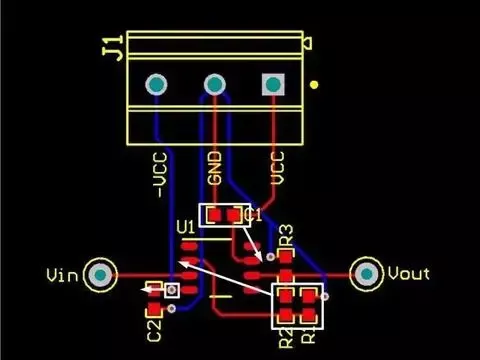

他們所做的首項改進(jìn)是將電阻R1和R2移至OPA191的倒相引腳(引腳2)旁;這樣有助于減小倒相引腳的雜散電容。

運算放大器的倒相引腳是一個(gè)高阻抗節點(diǎn),因此靈敏度較高。較長(cháng)的走線(xiàn)路徑可以作為電線(xiàn),讓高頻噪音耦合進(jìn)信號鏈。倒相引腳上的PCB電容會(huì )引發(fā)穩定性問(wèn)題。因此,倒相引腳上的接點(diǎn)應該越小越好。

將R1和R2移至引腳2旁,可以讓負荷電阻器R3旋轉180度,從而使去耦電容器C1更貼近OPA191的正電源引腳(引腳7)。讓去耦電容器盡可能貼近電源引腳,這一點(diǎn)極其重要。如果去耦電容器與電源引腳之間的走線(xiàn)路徑較長(cháng),會(huì )增大電源引腳的電感,從而降低性能。

他們所做的另一項改進(jìn)在于第二個(gè)去耦電容器C2。不應將VCC與C2的導孔連接放在電容器和電源引腳之間,而應布設在供電電壓必須通過(guò)電容器進(jìn)入器件電源引腳的位置。

圖3顯示了移動(dòng)每個(gè)部件和導孔從而改善布局的方法。

圖3 改進(jìn)布局的各部件位置

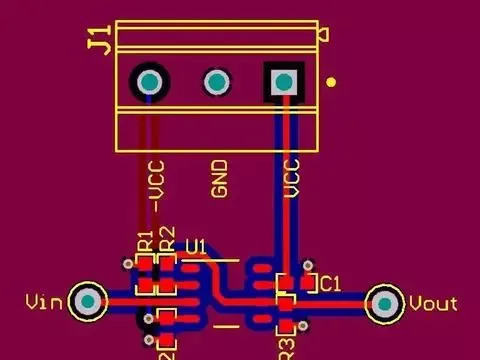

可以加寬走線(xiàn)路徑,以減小電感,即相當于走線(xiàn)路徑所連接的焊盤(pán)尺寸。還可以灌流電路板頂層和底層的接地層,從而為返回電流創(chuàng )造一個(gè)堅實(shí)的低阻抗路徑。圖4所示為終布局。

圖4 終布局

經(jīng)驗總結

當布設印刷電路板時(shí),務(wù)必遵循以下布設慣例:

1 盡量縮短倒相引腳的連接;

2 讓去耦電容器盡量靠近電源引腳。

3 如果使用了多個(gè)去耦電容器,將的去耦電容器放在離電源引腳近的位置。

4 不要將導孔置于去耦電容和電源引腳之間。

5 盡可能擴寬走線(xiàn)路徑。

6 不要讓走線(xiàn)路徑上出現90度的角。

7 灌流至少一個(gè)堅實(shí)的接地層。

8 不要為了用絲印層來(lái)標示部件而舍棄良好的布局。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問(wèn)題,請聯(lián)系小編進(jìn)行處理。

推薦閱讀: