與傳統的時(shí)鐘緩沖器相比����,運算放大器的一個(gè)優(yōu)點(diǎn)是具有靈活性��。運算放大器可以將時(shí)鐘脈沖進(jìn)行緩沖����、放大�����、失調���、反向�、相加�����、相減或濾波�。它們提供高輸入阻抗�、低輸入偏置電流�、低電源電流�����、獨立的省電模式(針對單個(gè)封裝中的多個(gè)放大器)���、低輸出阻抗�����,以及低傳播延遲��。

當在時(shí)鐘緩沖應用中使用運算放大器時(shí)�,設計者必須認識到并遵循一些工作限制��。以電壓反饋型放大器的增益帶寬積為例����,當放大器電路的閉環(huán)增益增加時(shí)��,它的帶寬會(huì )降低���,因此較大的增益意味著(zhù)較小的帶寬��。將多個(gè)低增益放大器進(jìn)行級聯(lián)以達到較高的帶寬����,由此確保信號路徑的總體增益和帶寬���。

單電源工作對于便攜式電子設備來(lái)說(shuō)是很重要的�。根據定義��,單電源運算放大器的輸入共模范圍包括負軌(地)�����,大部分甚至比地還低200mV���,但這并不表示輸出電壓的擺幅可以到地以下�����。典型軌對軌放大器的輸出級采用共發(fā)射極配置��。因此���,輸出電壓和軌電壓的最小差距是Vce(sat)����,其范圍可以從數十毫伏到數百毫伏���,具體取決于輸出負載�����。

幸運的是����,在這些應用中�,輸出電壓的擺幅通常不需要總是達到地電壓����。但是�,當輸入太接近地時(shí)(大約100mv~200mv)����,輸出級可能會(huì )達到飽和����,導致失真以及較長(cháng)的恢復時(shí)間�����。在直流耦合系統中��,應該確保信號電壓的低點(diǎn)高于200mV�����,或使用-200mV的負供電電壓��,這兩種方法都可以避免輸出級進(jìn)入飽和狀態(tài)�����。

放大器對裕量也有要求����,也就是其電壓的擺幅與正電源電壓之間能夠有多接近�����,因此還必須留意輸入共模范圍的高端�。如果輸入電壓太高�����,輸出電壓會(huì )失真并被截斷���。

ADA4850和ADA4851需要2.2V的裕量���,AD8061需要1.8V的裕量�����,而ADA4853僅需要1.2V的裕量���。

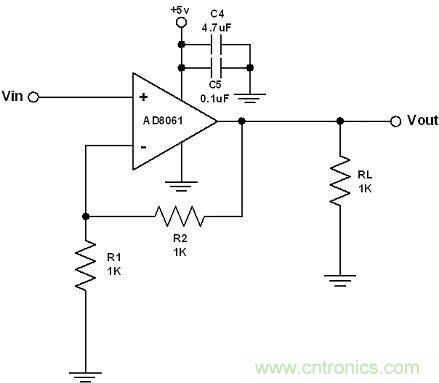

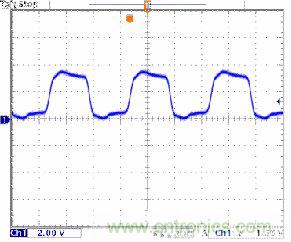

圖1所示的是一個(gè)增益為2的單電源同向運算放大器時(shí)鐘緩沖器��,圖2所示的是它的瞬態(tài)響應�。按照配置����,AD8061的上限約為33MHz�����,其2ns的傳輸延遲可與一些專(zhuān)用的時(shí)鐘緩沖器相媲美����。

圖1. 同向運算放大器時(shí)鐘緩沖器

圖2. 33MHz頻率下�,增益=+2的瞬態(tài)響應

在某些應用中可以使用交流耦合���,它允許使用更高帶寬的放大器以擴展頻率性能�。通過(guò)將輸入和輸出偏壓至電源電壓的中間值�����,這些放大器可被用于單電源應用中�。

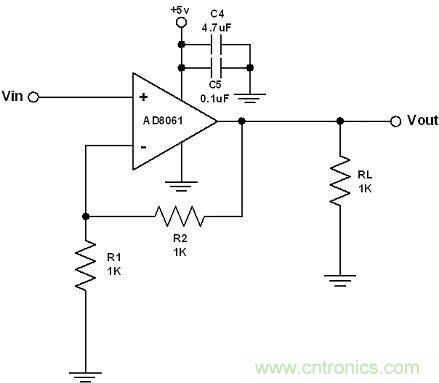

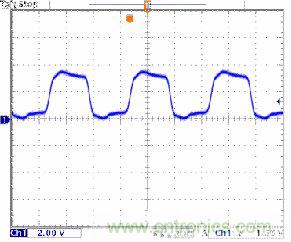

圖3所示的是使用AD8057高速放大器的設計��,這款器件具有325MHz帶寬和1150V/μs壓擺率�,在此電路設置為單位增益����。應當注意的是�,通過(guò)隔直電容C6后����,負載上的電壓與輸入信號Vin上的交流分量相等����,且不含直流分量�。這個(gè)電路的工作頻率范圍接近100MHz��。圖4所示的是時(shí)鐘響應����,可以看到當頻率高達90MHz時(shí)仍然可以維持較好的脈沖保真度�����。

圖3. 交流耦合時(shí)鐘緩沖器(單位增益)

圖4. 交流耦合時(shí)鐘緩沖器瞬態(tài)響應

如上所示�,當設計時(shí)鐘緩沖器時(shí)���,高速放大器往往能夠以更低的成本提供更多的靈活性���,在許多應用中都能夠同傳統的時(shí)鐘緩沖器相競爭�。針對具體的應用�����,還可以選擇使用單電源放大器或雙電源放大器��。